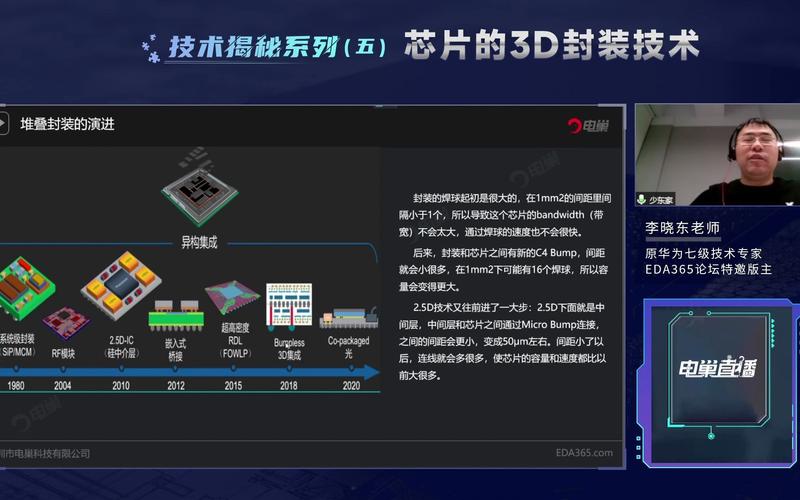

作为半导体封测领域领军企业,长电科技在多芯片堆叠封装技能领域有哪些创新实践?本文中将先容其技能上风、工艺和管控能力等内容。

多芯片堆叠封装技能上风

图1是两个不同类型的存储器封装的侧视图,从其封装构造我们可以看出,两个封装都是由多个芯片堆叠而成,目的是为了减少多芯片封装占用的空间,从而实现存储器件尺寸的最小化。个中较关键的工艺是芯片减薄、切割,以及芯片贴合。

从市场需求来看,倒装封装(FC)和硅通孔(TSV),以及晶圆级(wafer level)的封装形式可以有效地减鄙吝件尺寸的同时,提高数据传输速率,降落旗子暗记滋扰可能。但就目前的消费类市场需求来看,还是基于传统打线的封装形式仍占较大比重,其上风在于本钱的竞争力和技能的成熟度。

(a)DRAM多芯片封装侧视图 (b)NAND多芯片封装侧视图

图1多芯片封装侧视图

长电科技目前的工艺能力可以实现16层芯片的堆叠,单层芯片厚度仅为35um,封装厚度为1mm旁边。

多芯片堆叠封装关键工艺 之 芯片减薄、切割

1)研磨后切割 (Dicing after grinding,DAG)

紧张针对较厚的芯片(厚度需求>60um),属于较传统的封装工艺,成熟稳定。晶圆在贴上保护膜后进行减薄作业,再利用刀片切割将芯片分开。适用于大多数的封装。

图2 DAG (来源:DISCO)

2)研磨前切割 (Dicing before grinding,DBG)

紧张针对38-85um芯片厚度,且芯片电路层厚度>7um,针对较薄芯片的需求和存储芯片日益增长的电路层数(目前普遍的3D NAND层数在112层以上)。利用刀片先将芯片半切,再进行减薄,激光将芯片载膜 (Die attach film)切透。适用于大部分NAND 芯片,上风在于可以办理超薄芯片的侧边崩边掌握以及后工序芯片隐裂(die crack)的问题,大大提高了多芯片封装的可行性和可量产性。

图3 DBG (来源:DISCO)

3)研磨前的隐形切割 (Stealth Dicing before grinding,SDBG)

紧张针对35-85um芯片厚度,且芯片电路层厚度<7um,紧张针对较薄芯片的需求且电路层较少,如DRAM。利用隐形激光先将芯片中间分开,再进行减薄,末了将wafer崩开。适用于大部分DRAM wafer以及电路层较少的芯片,与DBG比较,由于没有刀片切割机器影响,侧边崩边掌握更佳。芯片厚度可以进一步降落。

图4 SDBG (来源:DISCO)

多芯片堆叠封装关键工艺 之 芯片贴合

1)芯片位置精度:由于多芯片堆叠的缘故,芯片贴合位置与芯片和芯片间的间隔掌握成为了工艺要点和难点。高精度贴合机台的引入,使得阶梯状一次性多芯片贴合精度可以担保在(+/-15um),可以有效地降落工艺良率丢失,以实现可量产的多芯片堆叠技能(如图5)。

图5 多芯片堆叠中的芯片贴合位置

2) 超薄芯片拾取:受限于芯片厚度,采取传统的顶针从芯片载膜(DAF)上剥离芯片,应力集中在只有1.5mil(38um)的芯片上,险些成为了不可能完成的任务。因此,针对超薄芯片的拾取,专门的治具被开拓出来。紧张的功能是通过多步平台突出将芯片从芯片载膜(DAF)上剥离。比较传统顶针,它将应力从点分散到面,从一步顶换改为多步顶。有效改进了超薄芯片的芯片隐裂问题。

多芯片堆叠工艺的管控

一、翘曲(Warpage)问题改进

晶圆经研磨后厚度哀求越来越薄,形变会导致晶圆无法连续后工序的作业,使得加工后的晶圆翘曲掌握成难堪题。通过SDBG和DBG,同时利用抛光工艺,开释晶圆表面应力,改进晶圆翘曲的情形。

二、异物、颗粒物的影响

只管目前的无尘车间级别已经达到1k级(微尘数量被严格掌握在每立方米1000个以内),封装车间中的异物、颗粒物对付超薄芯片来说,在每个工序中都是很大的威胁。如下图6,异物或颗粒物落在芯片上,受到外力挤压的情形下,就会导致芯片隐裂。

图6 异物,颗粒物带来的问题

因此,在关键工序(芯片干系),增加了负压设备HEPA环境,从而避免异物或颗粒物落在芯片表面。针对机台加盖,起到了双重防护的浸染。其余在芯片存放和运送中,利用指定料盒、推车和干燥柜。对指定料盒、推车和干燥柜加强定期洗濯频率均可减少异物、颗粒物的影响。

作为环球第三,中国大陆第一的芯片成品制造企业,长电科技始终对技能的研发和创新作为公司的重点发展计策,并取得一系列成果。长电科技拥有3200多项专利技能(截至2021年12月31日),荣获2020年度国家科学技能进步一等奖,在半导体家傍边始终发挥着行业龙头,技能引领的浸染。

展望未来,长电科技将连续强化创新,在芯片行业不断向精益化发展的过程中,研发包括多芯片堆叠封装技能等芯片成品制造技能,优化产品质量,不断提升自身的技能能力和做事能力,从而促进全体行业的发展。