锡须的危害

其余,在这里要先跟大家做个解释,在大电流和强电领域,一样平常无需担心锡须的存在,根据在实验室里测试的结果,随意马虎引起短路的锡须在通过30mA旁边的电流时就会熔断,因此在小电流和微功耗场合才须要特殊把稳。目前在电子设计领域,规避锡须的方案常日有两种:材料选择与PCB布局。

在物料清单(BOM)统计阶段,首先根据实际情形列出金属部件,逐一对应查看产品规格书(datasheet),清楚每种合金的组合以及镀膜。根据以往的履历以及可靠性测试来看,镀锡的材料最随意马虎产生锡须,镀铅和镀镍则有小概率情形涌现晶须,而经由氧化工艺的金属部件则比较稳定,没有涌现晶须,因此在金属材料的工艺上,要合理地选择。

不同材料的实验结果

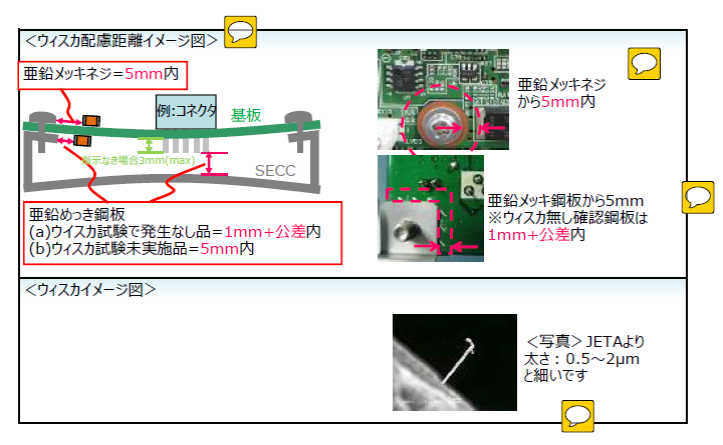

PCB布局理解清楚锡须的危害,在PCB设计上就可以利用间距和遮挡等手段来规避了,限于物料本钱的考虑,常日的做法是让板内元器件保持与金属部件的间距,这个间距标准是根据实验室大量测试验证得出来的数据,给大家作为参考:螺帽的半径5mm内不能放置元器件;金属垫片等部件要与板内的元器件间隔大于1mm。如果是工业产品,对爬电间距有严格哀求的,只要间距大于或者即是以上两种情形,都是符合哀求的。

PCB布局建议

在担保了材料的精确选择以及通过PCB合理布局规避了之后,锡须所导致的短路风险已经降到了普通产品可以接管的范围,但如果是分外行业的高标准产品,对产品设计初期的风险掌握有着极高的哀求,那就须要加入被动的保险方法了,比如在关键的电路上做过流保护,增加保险丝等,还有万一涌现短路动怒的情形,该从哪些方面来做规避方法呢?下一篇将会深入地给大家先容。

有关电子学领域的履历分享,系统知识的研究与剖析报告,欢迎连续关注电子学,我是李工。