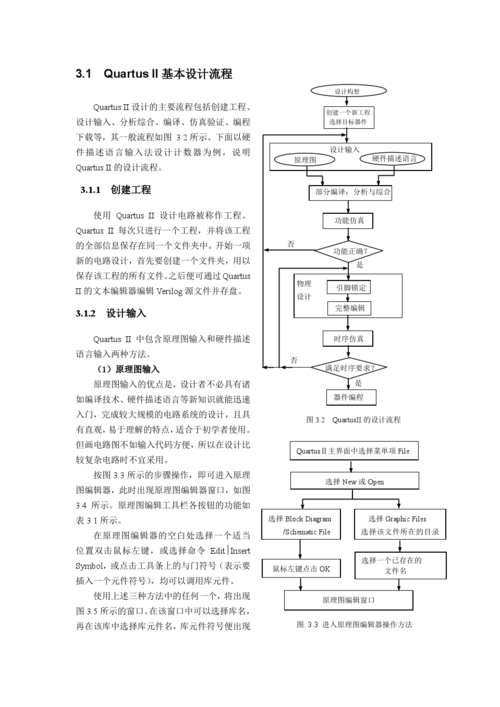

本文以大略的26位分频器工程实例为原本,从头至尾演示工程建立的所有细节及把稳事变,以便新手用户快速节制QuartusII的入门操作知识

二、声明

本文以ALTERA QuartusII11.0版本进行演示,虽然是针对CPLD EPM240T100开拓平台所做的入门辅导书,但这些流程对付FPGA设计是完备通用的。其余,本文在行文时描述的QuartusII步骤操作,均利用菜单办法,事实上,大多数操作可以直策应用工具栏上的快捷按钮,读者可自行熟习,实行的结果与菜单操作都是同等的

三、基本思路

工程实例建立的基本步骤如下:

(1)工程建立:建立与您的开拓平台相对应的工程,比如您的开拓平台是EPM3064,则后续的工程开拓也该当基于该芯片进行

(2)逻辑设计:这里包括很多设计手段,如AHDL、VHDL、Verilog HDL、事理图等等 ,由于本文讲的是QuartusII设计流程,不会过多关注此步骤

(3)逻辑综合:逻辑综合用于宏不雅观上您设计的逻辑判断是否有错,同时剖析出逻辑设计中的IO引脚,以便后续进行IO引脚的分配

(4)引脚分配:将逻辑设计中的IO分配到实际器件中的IO引脚

(5)逻辑编译:全编译工程逻辑,并天生可用于下载的烧录文件

(6)逻辑下载:将逻辑下载到实际的开拓平台中进行验证或利用

四、工程建立

下面我们来详细描述一个实际工程是如何建立的:

(1)打开QuartusII后,初始界面应如下图所示:

(2)选择菜单【File】→【New Project Wizard…】后,即可弹出如下图所示的新工程引导对话框:

设置工程目录位于D:/demo,并将工程名命名为“demo”,同时软件会自动将顶层设计模块名添补为“demo”,由于QuartusII的工程名必须与顶层设计文件的模块名同等,否则编译将出错

(3)选择【Next >】后,即可进入如下图所示的添加文件页表。此页表适用于源码文件已经准备无缺的情形,这样直接添加源文件即可将其加入当前工程。本文为了更详细展示设计流程,重新建立源码文件,不进行添加操作。

(4)选择【Next >】后,即可进入如下图所示的器件选择页表项。您的开拓平台是什么芯片型号,就在此页表选择相对应的器件型号,如果选择的器件型号与您实际利用的芯片型号不一致,在逻辑下载步骤时将会出错(如果你手头没有开拓板,只是为了学习HDL措辞或熟习软件,随意选择一个资源多点的就可以,防止由于HDL逻辑规模太大资源不足用而涌现编译缺点)。

由于ALTERA的器件非常多,因此QuartusII供应一些过滤选项,以帮忙我们快速找到对应的器件。本文的开拓平台芯片型号为“EPM240T100I5N”,该芯片为MAXII系列(Family),封装(Package)为“TQFP”,引脚数量(Pin count)为“100”,速率等级(Speed grade)为“5”,如下图所示:(对付EPM3032/3064或FPGA也是同样的方法,如果您按照此对话框设置后,没有找到您须要的器件型号,解释您可能没有安装该芯片对应的器件库)

对付本工程实例,设置好器件型号后,就可以直接选择【Finish】即可进入“第五节逻辑设计”即可,但如果您想理解其它页表项,可连续往下阅读。

(5)选择【Next >】后即可进入EDA工具设置页表项。QuartusII支持很多第三方工具,比如综合工具、仿真工具等等,第三工具常日在某一方面更为专业,特殊是仿真工具,QuartusII已经不再供应仿真功能,只能用第三方仿真工具,如Modelsim来进行仿真。

由于我们的实例比较大略,且仅看重开拓流程,因此我们对此步骤不做调度(后续我们将详述)

(6)选择【Next >】后,即可进行进入如下图所示的总结(Summary)页表,这里简要显示了您之前所做的所有设置,如果没有问题的话,选择【Finish】即可

五、逻辑设计

工程建立完成后,就可以开始动手进行逻辑的设计了

(1)选择菜单【File】→【New…】即可弹出如下图所示的新建(New)对话框,QuartusII支持很多的逻辑设计输入办法,这里我们选择“Verilog HDL File”,表示我们将利用Verilog HDL措辞作为本工程的逻辑设计输入办法。

(2)选择【OK】后,QuartusII将默认新建一个名为“Verilog1.v”的文件,我们将工程示例代码拷贝进去,此时应如下图所示:

把稳:这个源代码的模块名demo是与左边Project Navigator中工程名是同等的,而且是必须的

(2)选择菜单【File】→【Save】后,将文件保存在工程目录,并将其命名为“demo.v”即可,如下图所示:

把稳:文件名不一定必须是“demo.v”,QuartusII只哀求模块名与工程名相同,不哀求与文件名相同

完成后此时应如下图所示:

六、逻辑综合

逻辑设计完毕后,可以初步对逻辑进行综合,以判断是否有诸如语法缺点、逻辑缺点等非常,并可初步对IO引脚进行剖析

(1)选择菜单【Processing】→【Start】→【Start Analysis & Synthesis】后,即可开始进行逻辑设计的综合过程,完成后应如下图所示:

(2)菜单选择【Tools】→【Netlist Viewers】→【RTL Viewer】后即可涌现RTL(寄存器传输级)图,常日,对付大略的逻辑缺点,利用RTL可以看出来。本文要实现的是26位分频器,下图表示,每到来一个时钟,即利用Add0加法器将当前tmp寄存器中的值累加1,再通过一个clk_out~reg0将最高位输出,这恰好应证了我们的设计思路。

七、引脚分配

逻辑综合如果顺利的话,设计中的输入输出引脚信息已经被剖析出来,我们要做的便是将逻辑中的引脚分配到实际器件的引脚

(1)选择菜单【Assignments】→【Pin Planner】后,即可打开PinPlanner对话框。我们根据EPM240T100开拓板规格书中的引脚解释(对付任何一块开拓板,都必将有一个开拓板的事理图或接口引脚号的解释书,用来描述开拓板上主芯片与外围的连接关系),将其引脚如下图所示分配即可:

八、逻辑编译

引脚分配完成后,就可以对工程进行全编译,这包括逻辑综合、适配、时序剖析等步骤,本文暂不关注这些细节

(1)选择菜单【Processing】→【Start Compilation】后,即可开始全编译过程,如果顺利的话,将如下图所示:

在总结中显示了当前工程编译后所占用的资源情形,本工程利用51个宏单元,占用总设计资源的21%,利用了2个引脚(即clk与clk_out),占用总引脚的3%

九、逻辑下载

逻辑全编译后即可天生下载文件,对付CPLD开拓平台,常日是.pof文件,对付FPGA开拓平台,还可以是.sof、.jic等文件

(1)选择菜单【Tools】 → 【Programmer】后,在弹出的对话框中勾选“Program/Configure”,表示我们将要进行烧录操作,此时应如下图所示:

如果您没有插高下载器或下载器有非常,上图中USB-Blaster[USB-0]处将会显示“NoHardware”,这时您该当看看驱动是否安装,或下载器是否正常,如果确定都正常,可以点击左侧的Hardware Setup…按钮,弹出的对话框中列表中将有Usb blaster项,点击即可。

(2)将开拓平台按规格书所述供好电源,再精确插上USB-Blaster JTAG口,点击【Start】按钮即可开始进行文件烧录过程,烧录顺利后应如下图所示: