小电源(PCB设计中的电流比较小的电源)在设计中常日须要考虑旗子暗记完全性和电源分布的问题。在布局时,优先在旗子暗记层(常日是内层)铺铜,以供应地平面或电源平面的连接,以及旗子暗记的传输路径。这样可以有效地减少旗子暗记的串扰和传输延迟,提高旗子暗记质量。

然而,有时在旗子暗记层铺铜可能受到空间限定或其他设计哀求的影响,因此须要通过走线连接来知足小电源的分布需求。这种情形下,须要把稳以下几点:

走线方案:确保电源走线的路径短、宽度足够大,以降落电阻和电压降,并减少电磁滋扰。避免走线穿越高速旗子暗记线或者敏感的仿照部分,以免滋扰它们的正常事情。

地区域设计:在布局中,留出适当的地区域来放置电源分配网络元件(例如电容、电感等),以确保电源的稳定性和噪声抑制。

层间连接:如果在旗子暗记层无法知足电源分布的需求,可以考虑通过层间连接来实现。这可能包括通过通过孔(vias)连接到其他层上的地平面或电源平面,以供应更好的电源分布。

分区设计:将电源分布和旗子暗记区域划分身分歧的区域,并在布局中只管即便将它们分开,以减少相互关扰的可能性。这样可以更好地管理旗子暗记完全性和电源噪声。

综合考虑:在布局设计过程中,须要综合考虑旗子暗记完全性、电源分布、EMI(电磁滋扰)等成分,并根据详细的运用需求进行权衡和优化。

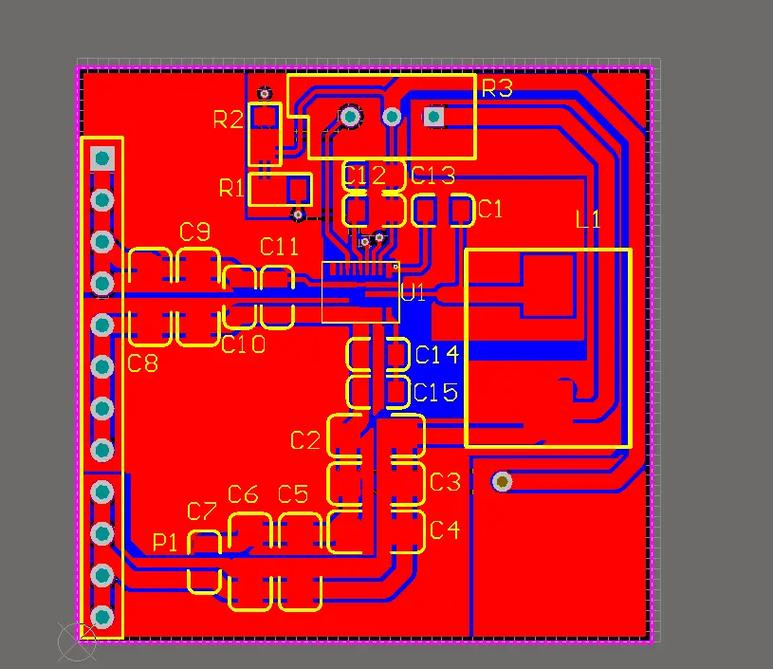

b) 12V、5V 电源如果是开关电源的输入电源,优先在旗子暗记层处理掉(表层、内层旗子暗记层),如果一定要在平面层分割,不要用作主要旗子暗记线的参考平面;这样可以有效减小此类“高”压对旗子暗记的影响;

开关电源的输入电容纹波过大的话,会导致一些危害。

12V上的开关纹波耦合到了1V1平面。

本板的处理器为X86处理器。X86处理的core电压为符合规范的VID电源。VID电源的电流比较大,由12V电源经由DCDC而产生。而这个VID电源的MOS管的开关噪声影响了前级的输入12V。所有的DCDC输入都是这个12V的电源网络,以是这个开关电源反复开关产生的很大的对外的滋扰。而1.1V的相邻的电源平面为12V,12V上的滋扰耦合到了1.1V平面。

c) 如果分割出的电源平面用作旗子暗记的参考平面,电源平面优先作为用电模块的旗子暗记参考平面;如果有多个电源,优先参考电压低的电源;例如 DDR3,利用的是 1.5V 电 源,则 1.5V 电源平面可以用作 DDR3 模块的旗子暗记参考平面,但不要参考其他电源;(常日 DDR3 数据参考地平面,地址掌握旗子暗记参考其电源平面)

d) 电源平面和地平面紧相邻,如果电源平面相邻的是旗子暗记层,只管即便在旗子暗记层多补一些 GND 铜,并打 GND 过孔;

在PCB设计中,电源平面和地平面紧密相邻的布局是为了供应更好的电源分配和地引线。当电源平面相邻的是旗子暗记层时,为了减少电源平面和旗子暗记层之间的串扰和噪声,会采纳以下方法:

增加地铜:在旗子暗记层只管即便增加地铜,这可以通过在旗子暗记层铺设地铜来实现。增加地铜有助于减少旗子暗记层与电源平面之间的电磁耦合,并供应更好的电磁屏蔽效果。

GND过孔:在旗子暗记层与电源平面之间打上GND过孔。这些过孔将旗子暗记层的地引线直接连接到地平面,有效地减少了地回流路径的电阻,降落了旗子暗记线的地电位颠簸,减少了地回流路径上的电流循环。

通过这些方法,可以最大程度地降落旗子暗记层与电源平面之间的串扰和噪声,提高旗子暗记的质量和稳定性。这种布局设计有助于担保电路的性能,并减少潜在的滋扰和问题。

e) 分割线宽度要合理;分割线宽度和两个电源的电压差有关,一样平常推举:模数之间分割宽度:25mil;数字之间分割宽度 15mil,局部可以更小一些;分割线宽度也可以根据板上空间情形灵巧调度,原则上越大越好;

f) 机壳地分割隔离宽度优先 2mm,局部根据情形调度,一样平常哀求不小于 1mm;其他 旗子暗记阔别机壳地,包括旗子暗记线、过孔、铺铜等;

g) 如果电源/地平面有分割,把稳相邻旗子暗记层旗子暗记线不要跨分割,只管即便避免分割开的参考平面上有高速旗子暗记的超过。

h) 分割的电源过孔避开隔离带,隔离带避铜,会导致此类电源过孔没有连接;

i) 仿照区域的电源,为了减小电源对旗子暗记的影响,一样平常不推举大面积铺电源网络铜, 一样平常是在旗子暗记层处理掉,电源铺铜或者走线知足载流即可,其他区域只管即便多铺地铜 和打地过孔;

j) 高压电源和低压电源要分区,间距越大越好;避免高压滋扰低压电源和旗子暗记;

k) 常见的爬电避让间距:

i. 电压<24V 时,表层盖阻焊、间距≥0.13mm;表层不盖阻焊、间距≥0.64mm

ii. 24V≤电压<48V 时、低级侧间距≥0.5mm,次级侧间距≥0.2mm;

iii. 48V≤电压<100V 时,间距≥1mm

iv. 100V≤电压<200V 时,间距≥1.5mm

v. 200V≤电压<400V 时,间距≥2.5mm

vi. 400V≤电压<600V 时,间距≥3.2mm

vii. 电压≥600V 时,间距≥5mm

l)确认电源、地能承载足够的电流。过孔数量是否知足承载哀求

(估算方法:外层铜厚1oz时1A/mm线宽,内层0.5A/mm线宽)

m)为降落平面的边缘辐射效应,在电源层与地层间要只管即便知足20H原则。

(条件许可的话,电源层的缩进得越多越好)。

“20H原则”是指要确保电源平面边缘比地平面(0V参考面)边缘至少缩进相称于两个平面之间间距的20倍,个中H便是指电源平面与地平面之间的间隔,如下图。

为什么须要20H原则?

在高速PCB中,常日电源平面和地平面间相互耦合RF能量成为边缘磁通透露情形,而且RF能量(RF电流)会沿着PCB边缘辐射出去,为了减少这种耦合效应,所有的电源平面物理尺寸都要比最近邻的地平面尺寸小20H。

n)如果存在地分割,检讨避免分割的地是否不构成环路?

o)相邻层不同的电源平面是否避免了交叠放置?

p)保护地、GND的隔离是否大于4mm?

q)靠近带连接器面板处是否布10~20mm的保护地,并用双排交错孔将各层相连?

r)电源走线有效宽度检讨:正负片铜是否有打断(BGA、过孔密集、以及过孔密集处是否有高速总线),需重点关注0.8mmBGA。

我对PCB设计的认知提升过程【1】兴趣驱动热爱

我对PCB设计的认知提升过程【2】硬件工程师要不要自己画PCB

我对PCB设计的认知提升过程【3】PCB走线该当走多长?

我对PCB设计的认知提升过程【4】PCB走线该当走多宽?

我对PCB设计的认知提升过程【5】PCB的内电层

我对PCB设计的认知提升过程【6】过孔

我对PCB设计的认知提升过程【7】PCB能不能走锐角和直角?

我对PCB设计的认知提升过程【8】去世铜是否要保留?(PCB孤岛)

我对PCB设计的认知提升过程【9】焊盘上是否可以打过孔?

我对PCB设计的认知提升过程【10】PCB材料、FR4到底是指什么材料?

我对PCB设计的认知提升过程【11】阻焊层,绿油为什么多是绿色

我对PCB设计的认知提升过程【12】钢网

我对PCB设计的认知提升过程【13】预布局

我对PCB设计的认知提升过程【14】PCB布局、布线 的办法

我对PCB设计的认知提升过程【15】跨分割走线

我对PCB设计的认知提升过程【16】旗子暗记的反射

我对PCB设计的认知提升过程【17】脏旗子暗记

我对PCB设计的认知提升过程【18】沉金、镀金、喷锡等表面处理工艺

我对PCB设计的认知提升过程【19】线距

我对PCB设计的认知提升过程【20】电容的摆放位置

我对PCB设计的认知提升【21】串扰

PCB的飞针测试

FPC概述及仿真

为什么PCB变形波折?如何办理?

一文搞懂“特色阻抗”

PCB的叠层设计

高速电路PCB回流路径