首先,晶圆制备包括衬底制备和外延工艺两大环节。衬底(substrate)是由半导体单晶材料制造而成的晶圆片,有硅、碳化硅、蓝宝石、氮化硅等材料,衬底可以直接进入晶圆制造环节生产半导体器件,也可以进行外延工艺加工生产外延片。外延(epitaxy)是指在经由切、磨、抛等仔细加工的单晶衬底上成长一层新单晶的过程,新单晶可以与衬底为同一材料,也可以是不同材料(同质外延或者是异质外延)。由于新生单晶层按衬底晶相延伸成长,从而被称之为外延层(厚度常日为几微米),而长了外延层的衬底称为外延片(外延片=外延层+衬底)。器件制作在外延层上展开。

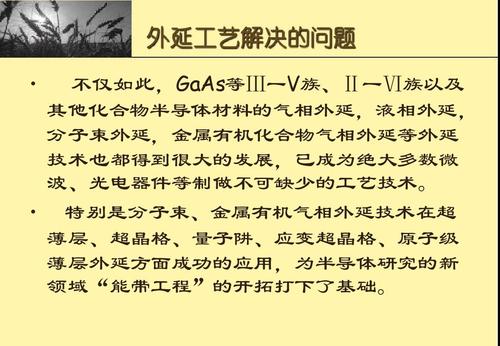

对付传统的硅半导体家当链而言,在硅片上制作器件(特殊是高比年夜功率)无法实现集电区高击穿电压,小串联电阻,小饱和压降要小的哀求。而外延技能的发展则成功地办理了这一困难。办理方案是在电阻极低的硅衬底上成长一层高电阻率外延层,器件制作在外延层上,这样高电阻率的外延层担保了管子有高的击穿电压。此外,GaAs等Ⅲ-Ⅴ族、Ⅱ-Ⅵ族以及其他分子化合物半导体材料的气相外延、液相外延等外延技能也都得到很大的发展,涌现了分子束、金属有机气相外延技能。

就第三代半导体器件而言,这类半导体器件险些都做在外延层上,碳化硅晶片本身只作为衬底。SiC外延材料的厚度、背景载流子浓度等参数直接决定着SiC器件的各项电学性能。因此,碳化硅外延技能对付碳化硅器件性能的充分发挥具有决定性的浸染,是宽禁带半导体家当主要的一环。